# **STLC7545**

# **ENHANCED V.34 BIS ANALOG FRONT-END**

PRELIMINARY DATA

- FULL ECHO CANCELLING CAPABILITY

- FULLY COMPATIBLE WITH THE ST7544

- ■16-BIT OVERSAMPLING A/D AND D/A CONVERTERS

- Programmable down-sampling frequency from 7200 to 22kHz.

- Sampling frequency can be 3, 4, 6, 8, 12, 16 x symbol rate

- Programmable Over sampling frequency (128, 160 or 192 x sampling frequency).

- The STLC7545 can work with external oversampling

- Programmable symbol rate (600, 1200, 1600, 2400, 2560, 2743, 2800, 2954, 3000, 3200, 3429 and 3491).

- Bit rates of 300bps, 600bps, 1200 and all multiples of 2400bps up to 38400bps can be generated.

- Dynamic range: 92dB with a sampling frequency 9600Hz, oversampling ratio 160.

- Total harmonic distortion: -89dB.

- ON CHIP REFERENCE VOLTAGE

- THREE PROGRAMMABLE DIGITAL FILTERS SECTIONS (up to 14th order each, coefficients loaded into RAM):

- Tx interpolation filter

- Rx decimation filter

- Rx reconstruction filter

- ANCILLARY CONVERTERS FOR EYE-DIAGRAM MONITORING

- ■CLOCK SYSTEM BASED ON DIGITAL PHASE LOCKED LOOPS

- Separate Tx DPLL and Rx DPLL

- Terminal clock input for Tx synchronization on all multiples of 2400Hz (VFast synchronization mode) or on sub-multiple of baud rate (7544 synchronization mode)

- Bit, Baud, sampling and highest synchronous clock outputs

- Maximum master clock frequency is 38MHz

- SINGLE OR DUAL SYNCHRONOUS SERIAL INTER-FACE TO DSP

- ANALOG POWER SUPPLY VOLTAGE: +5V

- DIGITAL POWER SUPPLY FROM 3.3V TO 5V

- LOW POWER CONSUMPTION:

- 100mW operating power at the nominal crystal frequency of 36.864MHz (digital supply at 3.3V)

- Less than 5mW in the Low-Power Reset Mode

- 0.7µm CMOS PROCESS

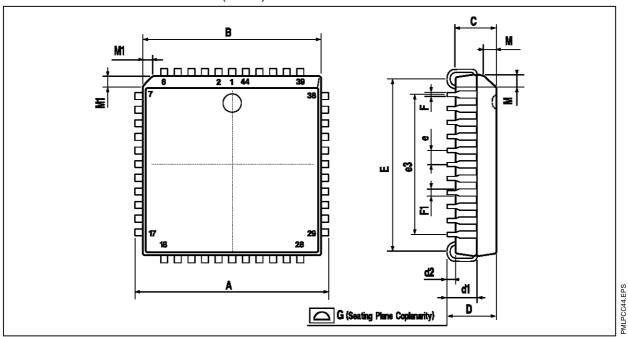

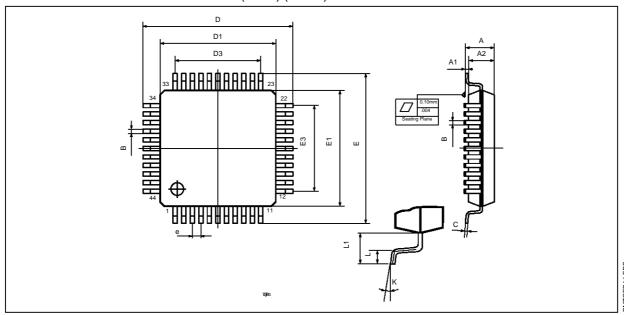

- PLCC44 OR TQFP44 (1.4mm body thickness)

#### **DESCRIPTION**

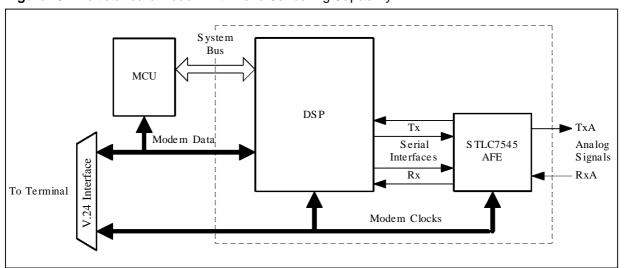

The STLC7545 is a single chip Analog Front-End (AFE) designed to implement high speed voice-grade Modems up to 38400 bps with echo cancelling capability.

Associated with one or several Digital Signal Processors (DSP), it provides a powerful solution for the implementation of multi-mode Modems meeting CCITT (V.17, V.21, V.22, V.22 bis, V.23, V.26, V.27, V.29, V.32, V.32 bis, V.33, V.34 and V.34 bis) and BELL (103, 202, 212A...) recommendations. It is fully compatible with the ST7544 and is also well suited emerging applications involving bit rates up to 38400 bps (in the VFast synchronization mode).

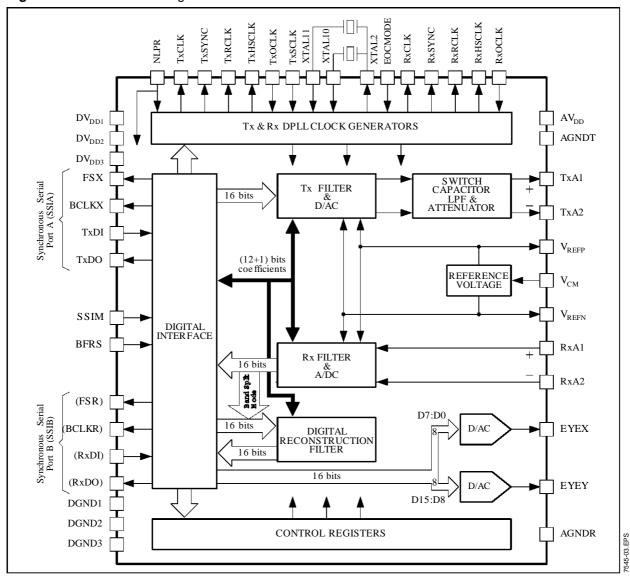

The transmit section includes a 16-bit over-sampling D/A converter with a programmable interpolating filter. The receive section includes a 16-bit oversampling A/D converter with two programmable filters (one for decimation and the other for reconstruction). Oversampling ratio is selectable to either 128, 160 or 192. Two additional 8-bit D/A converters allow eyediagram monitoring on a scope for modem performance adjustment.

Two independant clock generator systems are provided, one synchronized on the Tx rate and the other on the Rx rate.

In External Clock Mode, external oversampling clocks can be provided to the chip.

Two independent synchronous serial interfaces (SSI) allow several versatile ways of communicating with standard DSPs.

To save power, e.g. in lap-top modem applications, the lowpower reset mode can be used to reduce the power consumption to less than 5mW.

April 1996 1/53

# STLC7545

| TABLE OF CONTENTS Pag                                                                                            |                                                                                                                                                                                                                                                                |                                              |  |  |  |  |  |

|------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|--|--|--|--|--|

| ı                                                                                                                | PIN DESCRIPTION                                                                                                                                                                                                                                                | 5                                            |  |  |  |  |  |

| I.1                                                                                                              | PIN CONNECTIONS (Top View)                                                                                                                                                                                                                                     | 5                                            |  |  |  |  |  |

| 1.2                                                                                                              | PIN LIST                                                                                                                                                                                                                                                       | 6                                            |  |  |  |  |  |

| 1.3                                                                                                              | PIN FUNCTION                                                                                                                                                                                                                                                   | 7                                            |  |  |  |  |  |

| II                                                                                                               | BLOCK DIAGRAM                                                                                                                                                                                                                                                  | 10                                           |  |  |  |  |  |

| Ш                                                                                                                | FUNCTIONAL DESCRIPTION                                                                                                                                                                                                                                         | 11                                           |  |  |  |  |  |

| III.1                                                                                                            | SIGNAL TRANSFER BLOCK DIAGRAM                                                                                                                                                                                                                                  | 11                                           |  |  |  |  |  |

| III.2                                                                                                            | TRANSMIT D/A SECTION                                                                                                                                                                                                                                           | 12                                           |  |  |  |  |  |

| III.2.1<br>III.2.1.1<br>III.2.1.2<br>III.2.2                                                                     | Interpolation Filters. Programmable Interpolation Filter (IIR1) FIR Filter (FIR1). D/A Converter.                                                                                                                                                              | 12<br>12<br>12<br>12                         |  |  |  |  |  |

| III.3.                                                                                                           | Receive A/D Section                                                                                                                                                                                                                                            | 12                                           |  |  |  |  |  |

| III.3.1<br>III.3.2<br>III.3.2.1<br>III.3.2.2<br>III.3.3                                                          | A/D Converter.  Decimation Filters.  FIR Filter (FIR2)  Programmable Decimation Filter (IIR2)  Eye-diagram Display                                                                                                                                             | 12<br>12<br>12<br>13<br>13                   |  |  |  |  |  |

| III.4                                                                                                            | RECEIVE RECONSTRUCTION SECTION                                                                                                                                                                                                                                 | 13                                           |  |  |  |  |  |

| III.4.1<br>III.4.2                                                                                               | Programmable Interpolation Filter (IIR3)                                                                                                                                                                                                                       | 13<br>13                                     |  |  |  |  |  |

| III.5                                                                                                            | CLOCK GENERATION.                                                                                                                                                                                                                                              | 14                                           |  |  |  |  |  |

| III.5.1<br>III.5.2<br>III.5.2.1<br>III.5.2.2<br>III.5.3<br>III.5.4.1<br>III.5.4.2<br>III.6<br>III.6.1<br>III.6.2 | Transmit DPLL Transmit Clocks Internal Mode External Mode. Receive DPLL Receive Clocks Internal Mode External Mode External Mode External Mode External Mode. SERIAL INPUT/OUTPUT SYNCHRONOUS INTERFACES Tx Clock Related Registers Rx Clock Related Registers | 15<br>15<br>15<br>16<br>16<br>16<br>16<br>17 |  |  |  |  |  |

| IV                                                                                                               | SERIAL INTERFACE OPERATION                                                                                                                                                                                                                                     | 18                                           |  |  |  |  |  |

| IV.1<br>IV.2<br>IV.3<br>IV.4<br>IV.5                                                                             | DUAL SERIAL INTERFACE MODE (SSIA, SSIB)                                                                                                                                                                                                                        | 18<br>19<br>20<br>21<br>21                   |  |  |  |  |  |

| IV.6                                                                                                             | FRAME FREQUENCY PROGRAMMING.                                                                                                                                                                                                                                   | 21                                           |  |  |  |  |  |

| IV 7                                                                                                             | INITIALIZATION and LOW-POWER RESET MODE                                                                                                                                                                                                                        | 21                                           |  |  |  |  |  |

| TABLE (                      | OF CONTENTS (continued)                                              | Page     |

|------------------------------|----------------------------------------------------------------------|----------|

| V                            | CIRCUIT PROGRAMMING                                                  | 23       |

| V.1                          | MODE FIELD                                                           | 23       |

| V.2                          | ADDRESS FIELD                                                        | 23       |

| V.2.1                        | RAM Address Field.                                                   | 23       |

| V.2.2                        | Transmit Control Register Address Field                              | 23       |

| V.2.3                        | Receive Control Register Address Field                               | 24       |

| V.3                          | CONTROL REGISTER DATA FIELD                                          | 24       |

| V.3.1                        | Transmit Control Register Programming                                | 24       |

| V.3.2                        | Receive Control Register Programming                                 | 24       |

| V.3.3<br>V.3.3.1             | Control Bit Function Summary                                         | 25<br>25 |

| V.3.3.1<br>V.3.3.2           | RxCTRL Word                                                          | 25<br>25 |

|                              |                                                                      |          |

| VI                           | PROGRAMMABLE FUNCTIONS                                               | 26       |

| VI.1                         | TRANSMIT SECTION                                                     | 26       |

| VI.1.1                       | Transmit Bit Rate Clock Frequency Programming with FQ=36.864MHz      | 27       |

| VI.1.2                       | Transmit Bit Rate Clock Frequency Programming with FQ=25.8048MHz     | 27       |

| VI.1.3<br>VI.1.4             | Transmit Bit Rate Clock Frequency Programming with FQ=18.432MHz      | 28<br>29 |

| VI.1. <del>4</del><br>VI.1.5 | Transmit Sampling Clock Frequency Programming with FQ=36.864MHz      | 30       |

| VI.1.6                       | Transmit Sampling Clock Frequency Programming with FQ=25.8048MHz     | 30       |

| VI.1.7                       | Transmit Sampling Clock Frequency Programming with FQ=18.432MHz      | 30       |

| VI.1.8                       | Transmit Sampling Clock Frequency Programming. Divisor Rank          | 31       |

| VI.1.9                       | Transmit Baud Rate Frequency Programming. Divisor Rank               | 31       |

| VI.1.10<br>VI.1.11           | Highest Synchronous Transmit Frequency Programming. Divisor Rank     | 31<br>31 |

| VI.1.11<br>VI.1.12           | Transmit Synchronization Signal Programming                          | 31       |

| VI.1.12                      | Clock Mode Programming & R2 Divisor                                  | 32       |

| VI.1.14                      | Transmit Attenuator Programming                                      | 32       |

| VI.1.15                      | Phase Comparator Frequency and Decimation or Interpolation Ratio     | 32       |

| VI.1.16                      | Phase Shift Frequency                                                | 33       |

| VI.1.17                      | Transmit Test Programming                                            | 33       |

| VI.2                         | RECEIVE SECTION                                                      | 34       |

| VI.2.1                       | Receive Bit Rate Clock Frequency Programming with FQ=36.864MHz       | 35       |

| VI.2.2                       | Receive Bit Rate Clock Frequency Programming with FQ=25.8048MHz      | 35       |

| VI.2.3<br>VI.2.4             | Receive Bit Rate Clock Frequency Programming with FQ=18.432MHz       | 36<br>37 |

| VI.2.4<br>VI.2.5             | Receive Bit Rate Clock Frequency Programming. Divisor Rank           | 38       |

| VI.2.6                       | Receive Sampling Clock Frequency Programming with FQ=25.8048MHz      | 38       |

| VI.2.7                       | Receive Sampling Clock Frequency Programming with FQ=18.432MHz       | 38       |

| VI.2.8                       | Receive Sampling Clock Frequency Programming. Divisor Rank           | 39       |

| VI.2.9                       | Receive Baud Rate Frequency Programming. Divisor Rank                | 39       |

| VI.2.10                      | Highest Synchronous Transmit Bit Frequency Programming. Divisor Rank | 39       |

| VI.2.11                      | Receive Fine Phase Shift Programming                                 | 40       |

| VI.2.12<br>VI.2.13           | Receive Coarse Phase Shift Programming                               | 40<br>41 |

| VI.2.13<br>VI.2.14           | Receive Test Programming & R2 Divisor                                | 41       |

# STLC7545

| TABLE (            | OF CONTENTS (continued)                                       | Page     |

|--------------------|---------------------------------------------------------------|----------|

| VII                | ELECTRICAL SPECIFICATIONS                                     | 42       |

| VII.1              | ABSOLUTE MAXIMUM RATINGS (referenced to GND)                  | 42       |

| VII.2              | DC CHARACTERISTICS                                            | 42       |

| VII.2.1            | Power Supply And Common Mode Voltage                          | 42       |

| VII.2.2<br>VII.2.3 | Digital InterfaceCrystal Oscillator Interface (XTAL10,XTAL11) | 42<br>42 |

| VII.2.3<br>VII.2.4 | Analog Interface                                              | 42       |

| VII.3              | AC ELECTRICAL SPECIFICATIONS                                  | 44       |

| VII.3.1            | Serial Channel Timing                                         | 44       |

| VIII               | TRANSMIT CHARACTERISTICS                                      | 45       |

| VIII.1             | TEST CONDITIONS                                               | 45       |

| VIII.2             | PERFORMANCE OF THE TX CHAIN                                   | 45       |

| VIII.3             | SMOOTHING FILTER TRANSFER CHARACTERISTICS                     | 45       |

| IX                 | RECEIVE CHARACTERISTICS                                       | 46       |

| IX.1               | TEST CONDITIONS                                               | 46       |

| IX.2               | PERFORMANCE OF THE RX CHAIN                                   | 46       |

| X                  | TYPICAL APPLICATIONS                                          | 47       |

| X.1                | MULTI-STANDARD MODEM WITH ECHO CANCELLING                     | 47       |

| X.2                | LINE INTERFACE                                                | 47       |

| X.3                | COMMON MODE VOLTAGE GENERATION AND DECOUPLING                 | 48       |

| X.4                | CRYSTAL OSCILLATOR                                            | 48       |

| ΧI                 | ANNEXE A                                                      | 49       |

| XI.1               | IIR FILTER OPERATION                                          | 49       |

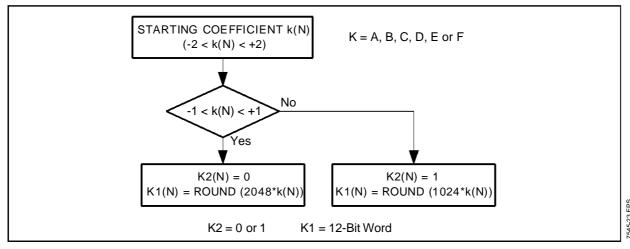

| XI.1.1             | COEFFICIENT ROUNDING                                          | 49       |

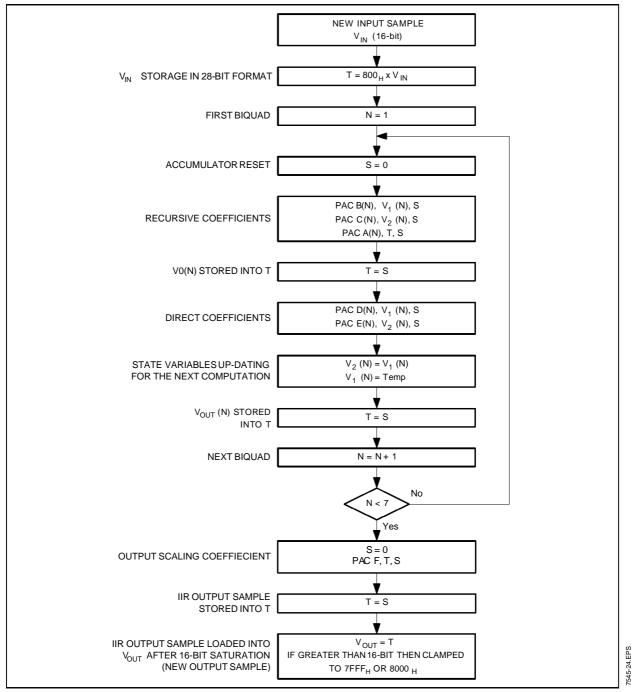

| XI.1.2             | DETAILED OPERATION                                            | 49       |

| ΥII                | PACKAGE MECHANICAL DATA                                       | 52       |

# I - PIN DESCRIPTION

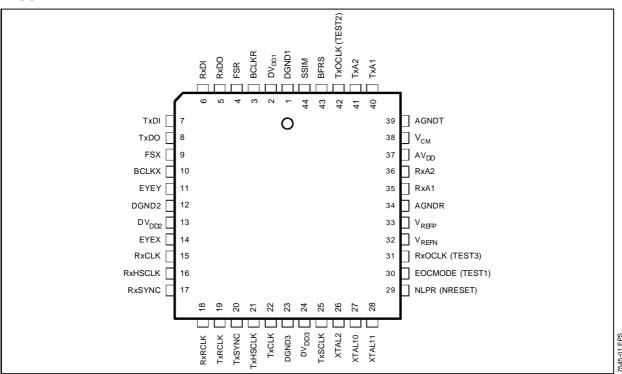

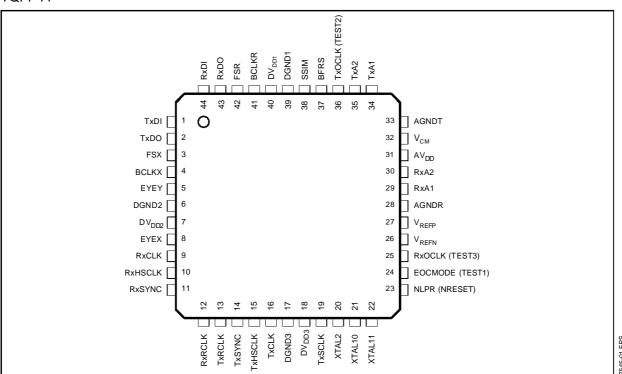

# I.1 - PIN CONNECTIONS (Top View)

# PLCC44

# TQFP44

$\textbf{Note:} \ \text{The pin names in the parenthesis are the corresponding for the ST7544}.$

# I.2 - PIN LIST

| PQFP | PLCC | NAME               | DESCRIPTION                                                                                                       |  |  |  |  |  |  |  |

|------|------|--------------------|-------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| 39   | 1    | DGND1              | Digital Ground (0V)                                                                                               |  |  |  |  |  |  |  |

| 40   | 2    | DV <sub>DD1</sub>  | Positive Digital Power Supply (3.15V to 5.25V)                                                                    |  |  |  |  |  |  |  |

| 41   | 3    | BCLKR              | Receive bit Clock Output                                                                                          |  |  |  |  |  |  |  |

| 42   | 4    | FSR                | Receive Frame Synchronization Output                                                                              |  |  |  |  |  |  |  |

| 43   | 5    | RxDO               | Receive Serial Data Output                                                                                        |  |  |  |  |  |  |  |

| 44   | 6    | RxDI               | Receive Serial Data Input                                                                                         |  |  |  |  |  |  |  |

| 1    | 7    | TxDI               | Transmit Serial Data Input                                                                                        |  |  |  |  |  |  |  |

| 2    | 8    | TxDO               | Transmit Serial Data Output                                                                                       |  |  |  |  |  |  |  |

| 3    | 9    | FSX                | Transmit Frame Synchronization Output                                                                             |  |  |  |  |  |  |  |

| 4    | 10   | BCLKX              | Transmit Bit Clock Output                                                                                         |  |  |  |  |  |  |  |

| 5    | 11   | EYEY               | 8 bit Y D/AC Output for Eye Pattern display                                                                       |  |  |  |  |  |  |  |

| 6    | 12   | DGND2              | Digital Ground (0V)                                                                                               |  |  |  |  |  |  |  |

| 7    | 13   | DV <sub>DD2</sub>  | Positive Digital Power Supply (3.15V to 5.25V)                                                                    |  |  |  |  |  |  |  |

| 8    | 14   | EYEX               | 8bit X D/AC Output for Eye Pattern display                                                                        |  |  |  |  |  |  |  |

| 9    | 15   | RxCLK              | Receive Bit Rate Clock Output                                                                                     |  |  |  |  |  |  |  |

| 10   | 16   | RxHSCLK            | Receive Highest Clock Output                                                                                      |  |  |  |  |  |  |  |

| 11   | 17   | RxSYNC             | Receive Synchronization Pulse Output                                                                              |  |  |  |  |  |  |  |

| 12   | 18   | RxRCLK             | Receive Baud Rate Clock Output                                                                                    |  |  |  |  |  |  |  |

| 13   | 19   | TxRCLK             | Transmit Baud Rate Clock Output                                                                                   |  |  |  |  |  |  |  |

| 14   | 20   | TxSYNC             | Transmit Synchronous Pulse Output                                                                                 |  |  |  |  |  |  |  |

| 15   | 21   | TxHSCLK            | Transmit Highest Clock Output                                                                                     |  |  |  |  |  |  |  |

| 16   | 22   | TxCLK              | Transmit Bit Rate Clock Output                                                                                    |  |  |  |  |  |  |  |

| 17   | 23   | DGND3              | Digital Ground (0V)                                                                                               |  |  |  |  |  |  |  |

| 18   | 24   | DV <sub>DD3</sub>  | Positive Digital Power Supply (3.15V to 5.25V)                                                                    |  |  |  |  |  |  |  |

| 19   | 25   | TxSCLK             | Transmit Synchronization Clock Input                                                                              |  |  |  |  |  |  |  |

| 20   | 26   | XTAL2              | Crystal Output                                                                                                    |  |  |  |  |  |  |  |

| 21   | 27   | XTAL10             | External Clock/Crystal Input 1                                                                                    |  |  |  |  |  |  |  |

| 22   | 28   | XTAL11             | External Clock/Crystal Input 2                                                                                    |  |  |  |  |  |  |  |

| 23   | 29   | NLPR               | Low Power Reset Input                                                                                             |  |  |  |  |  |  |  |

| 24   | 30   | EOCMODE<br>(TEST1) | External Oversampling Clock Mode Input. Must be tied to DGND in either the STLC7545 normal mode or the 7544 mode. |  |  |  |  |  |  |  |

| 25   | 31   | RxOCLK<br>(TEST3)  | Receive Oversampling Clock Input. Output high-impedance in normal mode.                                           |  |  |  |  |  |  |  |

| 26   | 32   | $V_{REFN}$         | 16 bit D/AC and A/DC Negative Reference Voltage                                                                   |  |  |  |  |  |  |  |

| 27   | 33   | $V_{REFP}$         | 16 bit D/AC and A/DC Positive Reference Voltage                                                                   |  |  |  |  |  |  |  |

| 28   | 34   | AGNDR              | Analog Ground (0V)                                                                                                |  |  |  |  |  |  |  |

| 29   | 35   | RxA1               | Receive Positive Analog Input                                                                                     |  |  |  |  |  |  |  |

| 30   | 36   | RxA2               | Receive Negative Analog Input                                                                                     |  |  |  |  |  |  |  |

| 31   | 37   | $AV_{DD}$          | Positive Analog Power Supply (+5V±5%)                                                                             |  |  |  |  |  |  |  |

| 32   | 38   | V <sub>CM</sub>    | Common Mode Voltage Output (2.5V ±10%)                                                                            |  |  |  |  |  |  |  |

| 33   | 39   | AGNDT              | Analog ground (0V)                                                                                                |  |  |  |  |  |  |  |

| 34   | 40   | TxA1               | Smoothing filter positive Output                                                                                  |  |  |  |  |  |  |  |

| 35   | 41   | TxA2               | Smoothing filter negative Output                                                                                  |  |  |  |  |  |  |  |

| 36   | 42   | TxOCLK<br>(TEST2)  | Transmit Oversampling Clock Input. Output high-impedance in normal mode.                                          |  |  |  |  |  |  |  |

| 37   | 43   | BFRS               | Bit Frame Rate Select Input                                                                                       |  |  |  |  |  |  |  |

| 38   | 44   | SSIM               | Serial Synchronous Interface Mode Input                                                                           |  |  |  |  |  |  |  |

Note: The pin names in brackets are the corresponding names for the ST7544.

#### **I.3 - PIN FUNCTION**

# I.3.1 - Power Supply (9 Pins)

#### Analog V<sub>DD</sub> Supply (AV<sub>DD</sub>)

This pin is the positive analog power supply ( $+5V\pm5\%$ ) for the Transmit and the Receive sections. It is not internally connected to digital  $V_{DD}$  supply ( $DV_{DD1-3}$ ).

### **Digital V<sub>DD</sub> Supply** (DV<sub>DD1</sub>,DV<sub>DD2</sub>,DV<sub>DD3</sub>)

These pins are the positive digital power supply (3.5V to 5.25V) for Transmit and Receive digital internal circuitry.

#### Analog Ground (AGNDT.AGNDR)

These pins are the analog ground return of the analog Transmit (Receive) section.

#### Digital Ground (DGND1,DGND2,DGND3)

These pins are the ground connections for Transmit and Receive internal digital circuitry.

Note 1: To obtain published performance, the analog  $V_{DD}$  and Digital  $V_{DD}$  should be decoupled with respect to AGND and DGND, respectively. The decoupling is intended to isolate digital noise from the analog section; decoupling capacitors should be as close as possible to the respective analog and digital supply pins.

**Note 2 :** All the ground pins must be tied together. In the following section, the ground and supply pins are referred to as GND and V<sub>DD</sub>, respectively.

#### I.3.2 - Clock and Control Signals (16 Pins)

External Clock/Crystal Inputs (XTAL10.XTAL11) XTAL10 and XTAL11 inputs must be tied to external crystal(s) or external clock(s). These inputs are selected from the TxCtrl register. The maximum clock rate is 38MHz. XTAL10 is the default External Clock/Crystal input. It is mandatory to shortcircuit XTAL10 and XTAL11 when a single external crystal or clock generator is used. The nominal master clock frequency is 36.864MHz (this frequency and the frequency 25.8048MHz are well suited for the V.34 application) but the onchip amplifier is designed for a parrallel crystal oscillator with a frequency equal to 18.432MHz. The other master clocks frequencies (18.432MHz, 25.8048MHz and 29.4912MHz) are well suited for the well known CCITT recommendations (V.21 through V.32bis).

#### Crystal Outputs (XTAL2)

This output is to be tied to one or two external crystals (see Figure 1). If an external clock is used, XTAL2 should be left open circuit.

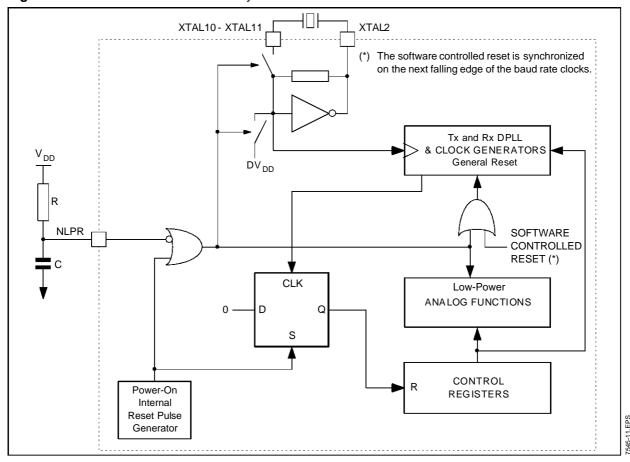

#### Low power and Reset Input (NLPR)

This pin , when low, synchronizes the STLC7545 clock system and puts it in low power mode. NLPR pin must be tied to  $V_{DD}$  during normal operation.

Access to the chip is disabled during power-on reset until the clock oscillator starts. The reset time duration can be increased by connecting the NLPR input to an external RC network (see Figure 9). The Low-Power Reset Mode is activated when this pin is tied to GND (Operation of all clocks and the analog section is stopped).

#### **Transmit Synchronization Clock Input (TxSCLK)**

This pin can be connected to an external terminal clock to phase-lock the internal transmit clocks. It can be disabled under software control to allow the Tx DPLL to free run or phase lock on the Rx clock system. To phase lock the TxDPLL there must be transition on TxSCLK input within FCOMP period when programming TxCR2 register.

#### **Transmit Bit Rate Clock Output (TxCLK)**

This pin outputs the synchronous transmit bit clock selected for the MODEM.

# Transmit Baud Rate Clock Output (TxRCLK)

This pin, when the bit D4 within receive register RxCR3 is set to 0, outputs the synchronous transmit baud rate clock (initial state). When bit D4 is set to 1 this pin outputs the frequency comparison signal FCOMP (used by the TxDPLL in both 7544 mode and V.Fast synchronization) when bit 0 of RxCR1 is set to 0 this output is disabled.

# **Transmit Synchronization Pulse Output** (TxSYNC)

This pin outputs the synchronization transmit reset pulse when a soft reset is applied to the STLC7545. Combined with TxHSCLK clock it can be used to externally provide any synchronous transmit clock.

# Transmit Highest Clock Output (TxHSCLK)

This pin outputs the highest synchronous transmit clock to provide any external or multiplexing clock when bit 0 of RxCR1 is set to 0 this output is disabled.

#### Transmit Oversampling Clock input (TxOCLK)

This input can be connected to an external clock to provide the chip with the over-sampling clock, depending on the External Over sampling Mode input (EOCMODE). In normal mode this pin should be static (tied to GND or VDD).

#### Receive Bit Rate Clock Output (RxCLK)

This pin outputs the synchronous receive bit clock selected for the MODEM.

#### Receive Baud Rate Clock Output (RxRCLK)

This pin outputs the synchronous Receive baud rate clock when bit 0 of RxCR1 is set to 0 this output is disabled.

# $\textbf{Receive Synchronization Pulse Output} \, (\texttt{RxSYNC})$

This pin outputs the synchronization receive reset pulse when a soft reset is applied to the STLC7545. Combined with RxHSCLK clock it can be used to externally provide any synchronous receive clock.

#### Receive Highest Clock Output (RxHSCLK)

This pin outputs the highest synchronous receive clock to give any external or multiplexing clock when bit 0 of RxCR1 is set to 0 this output is disabled.

# Receive Oversampling Clock input (RxOCLK)

This input can be connected to an external clock to provide the chip with the oversampling clock, depending on the External Over sampling Mode input Pin (EOCMODE). In normal mode this pin should be static (tied to GND or  $V_{DD}$ ).

# External Oversampling Clock Mode (EOCMODE)

This pin is used for selecting one of the two possible oversampling modes. When EOCMODE is tied to GND, all the clock are provided internally (mode compatible with the ST7544). When EOCMODE is tied to  $V_{DD}$ , the oversampling clocks must be input on TxOCLK and RxOCLK pins. The TxHSCLK (RxHSCLK) and TxSync (RxSync) signals along with external fractional divider can be used to provide the oversampling clocks to the STLC7545.

# **I.3.3 - Synchronous Serial Interfaces** (SSIA,SSIB) (10 pins)

# Serial Synchronous Interface Mode input (SSIM)

This input activates one or both serial interfaces. When SSIM is tied to  $V_{DD}$ , both A and B ports are functional: port A (SSIA) is dedicated to the Transmit channel and port B (SSIB) is dedicated to the Receive channel.

When SSIM is tied to GND only port A (SSIA) is selected. In this case SSIA carries both Tx and Rx Signals and EYE pattern.

#### Bit Frame Rate Select input (BFRS)

This input selects one of the two possible bit frequencies for the BCLKX and BCLKR clocks. When BFRS is tied to  $V_{DD}$  the BCLKX (BCLKR) frequencies are equals to the oversampling ratio (divider V Table 40) times the FSX (FSR) frequencies. When BFRS is tied to GND, BCLKX (BCLKR) frequencies are equal to V/2 times the FSX (FSR) frequencies.

# Frame Synchronization Transmit output (FSX) This output clock is the Transmit Frame synchronization pulse signal of the SSIA port which has

nominal frequency equal to the transmit sampling frequency. This pulse indicates the beginning of the 16-bit serial words on the serial data input/output port A.

### Bit Clock Transmit output (BCLKX)

This output pin provides the serial bit clock for the SSI port A. The BCLKX frequency equals V or V/2 times the Transmit sampling frequency, depending on the Bit Frame Select Input (BFRS).

#### Serial Data Transmit input (TxDI)

This input receives word-oriented serial data. Data is loaded from TxDI into the Transmit Shift Register (TSRIN) on the falling edge of BCLKX and transfered to the Transmit Buffer Register (TBRIN) when a complete 16 bit word has been received. Data is assumed to be received MSB first.

#### Serial Data Transmit output (TxDO)

This output sends word-oriented serial data. The 16 bit Data Word loaded in the Transmit Buffer Register (TBROUT) is transfered to the Transmit Shift Register (TSROUT) and clocked out of TSROUT on the rising edge of BCLKX. Serial words are transmitted MSB first.

#### Receive Frame Synchronization output (FSR)

This output clock is the Receive Frame synchronization pulse signal of SSI port B which has frequency equal to the receive sampling frequency. This pulse is used to indicate the beginning of serial words on the serial data input/output port B.

#### Receive Bit Clock output (BCLKR)

This output pin provides the serial bit clock for the SSI port B. The BCLKR frequency is V times or (V/2) times, selected by BFRS) the receive sampling frequency.

#### Receive Serial Data input (RxDI)

This input receives word-oriented serial data. Data is clocked from RxDI into the Receive Shift Register (RSRIN) on the falling edge of BCLKR and transfered to the Receive Buffer Register (RBRIN) when a complete 16-bit word has been received. Data is assumed to be received MSB first.

# Receive Serial Data output (RxDO)

This output sends word-oriented serial data. The 16-bit Data Word loaded in the Receive Buffer Register (RBROUT) is transfered to the Receive Shift Register (RSROUT) and clocked out of RSROUT on the rising edge of BCLKR. Serial words are transmitted MSB first.

#### I.3.4 - Analog Interface (9 pins)

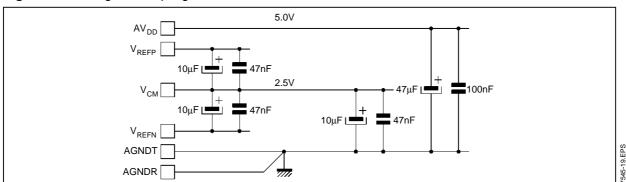

# D/AC and A/DC Positive Reference Voltage output $(V_{REFP})$

This pin provides the Positive Reference Voltage used by the 16-bit converters. The reference voltage,  $V_{REF}$ , is the voltage difference between the  $V_{REFP}$  and  $V_{REFN}$  outputs, and its nominal value is 2.5V.  $V_{REFP}$  should be externally decoupled with respect to  $V_{CM}$  (see Figure 17).

# D/AC and A/DC Negative Reference Voltage $(V_{REFN})$

This pin provides the Negative Reference Voltage used by the 16 bit converters, and should be externally decoupled with respect to  $V_{CM}$ .

#### **Common Mode Voltage Output (VCM)**

This output pin is the common mode Voltage (AV<sub>DD</sub>-AGND)/2 internally generated. This output must be decoupled with respect to AGND. This output pin could be forced externally (compatible with ST7544 application).

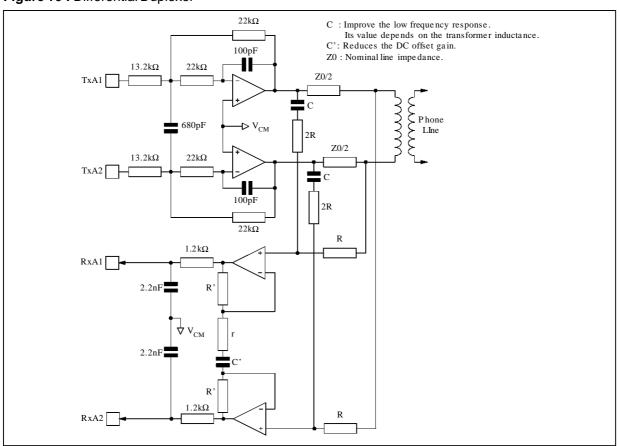

#### **Smoothing filter positive Output (TxA1)**

This pin is the positive output of the fully differential analog smoothing filter.

#### **Smoothing filter negative Output (TxA2)**

This pin is the negative output of the fully differential analog smoothing single pole switch capacitor filter. Outputs TxA1 and TxA2 provide analog signals

with maximum peak to peak amplitude 2 x V<sub>REF</sub>, and must be followed by an external continuous time two pole smoothing filter (see Figure 16). The smoothing filter order depends of the acceptable transmit signal spectrum on the line. The cut-off frequency of the external filter must be greater than two times the transmit sampling frequency (Fsx), so that the combined frequency response of both the internal and external filters is flat in the pass band

# Receive Positive Analog Input (RxA1)

This pin is the differential positive A/DC Input.

#### **Receive Negative Analog Input (RxA2)**

This pin is the differential negative A/DC Input. These analog inputs (RxA1,RxA2) are presented to the SigmaDelta modulator, the analoginput peak to peak signal range must be less than 2 x V<sub>REF</sub>, and must be preceded by an external continuous-time single pole anti-aliasing filter (see Figure 16). The cut-off frequency of the filter must be lower than one half the transmit over-sampling frequency (TxOSCK). These filters should be set as close as possible to the RxA1 (RxA2) pins.

#### D/AC output for Eye Pattern (EYEX,EYEY)

These pins are the outputs of two 8-bit digital to analog converters used to monitor, on a CRT, the X and Y quadrature signals of the eye pattern of the demodulated signal.

# **II - BLOCK DIAGRAM**

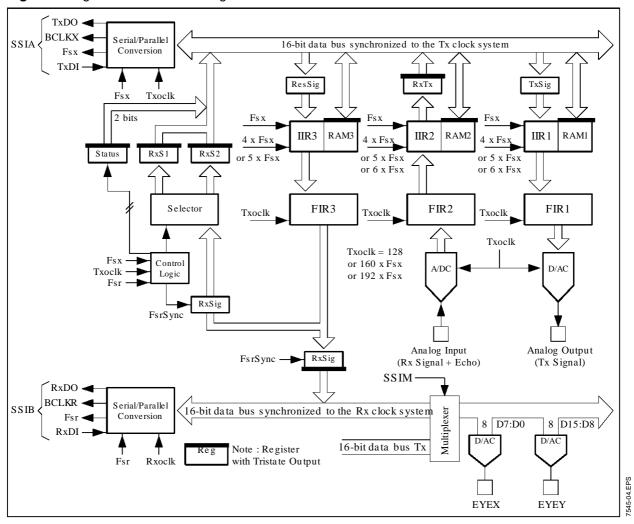

Figure 1: General Block Diagram

#### **III - FUNCTIONAL DESCRIPTION**

#### III.1 - SIGNAL TRANSFER BLOCK DIAGRAM

The STLC7545 Block Diagram illustrates three paths as follows: The Transmit D/A Section, the Receive A/D section and the Receive Reconstruction section.

Figure 2: Signal Transfer Block Diagram

#### **III.2 - TRANSMIT D/A SECTION**

The functions included in the Tx D/A section are detailed hereafter.

#### III.2.1 - Interpolation Filters

The oversampling is performed by two cascaded digital interpolating filters: IIR1 and FIR1. The IIR1 and FIR1 filters are sampled at 4 x Fsx and 128 x Fsx (5 x Fsx and 160 x Fsx) (6 Fsx and 192 x Fsx), respectively.

# III.2.1.1 - Programmable Interpolation Filter (IIR1)

IIR1 is an infinite impulse response interpolating filter.

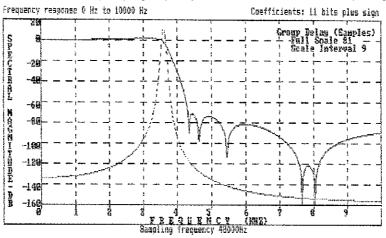

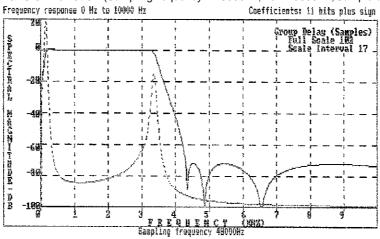

The purpose of this digital filter is to interpolate 4-times (5 times, 6 times) the digital signal coming from the DSP. This filter is sampled at the basic sampling frequency, (e.g. 9600 x 4 Hz), and must exhibit, as a minimum, a low-pass section which is mandatory to remove replicas above half the sampling frequency (e.g. 4800Hz) (see Figure 13).

The digital samples are encoded in 16-bit two's complement format.

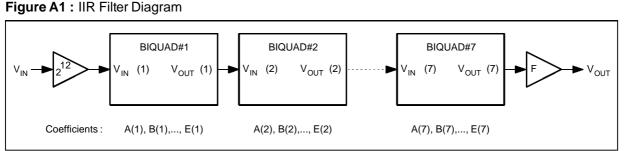

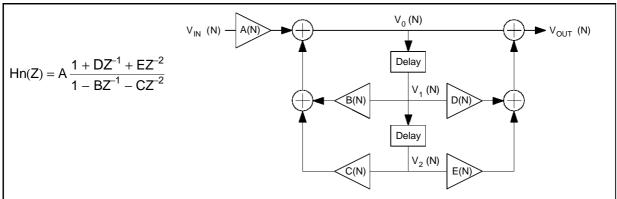

The IIR1 filter is a cascade of seven biquads (see Figure A1). The filter coefficients are loaded into the associated RAM (38 x 13). Each coefficient is coded into 12bits and can be doubled by virtue of an extra bit. All 38 coefficients have to be loaded to implement an IIR transfer function (see Annexe A).

This filter has been made programmable to offer each user the possibility to add filtering characteristics, e.g. high-pass section or equalization, matched to a particular application.

#### III.2.1.2 - FIR Filter (FIR1)

FIR1 is a finite impulse response interpolating filter. Its input sampling frequency is 4 x Fsx (or 5 x Fsx) (or 6 x Fsx) and its interpolation ratio is 32. The Z transfer function of this FIR is:

$$H(z) = \left(\frac{1 - z^{-32}}{32 (1 - z^{-1})}\right)^{3}$$

with  $Z = \exp(j2\pi F/Txoclk)$ and Txoclk = 128 (160, 192) x Fsx

#### III.2.2 - D/A Converter

The 128-times (160 times, 192 times) oversampled D/A converter includes a second order digital noise shaper, a one bit D/A converter and a single pole analog low-pass filter. The gain of the last output stage can be programmed to 0dB,-6dB or infinite attenuation. The cut-off frequency of the single pole switch-capacitor low-pass filter is:

fc-3dB=Txoclk /(2 x

$$\pi$$

x 10)

where Txoclk = 128 (160, 192) x Fsx

Continuous-time filtering of the analog differential output is necessary using an off-chip amplifier and a few external passive components (see Figure 16).

At least 86dB signal to noise plus distortion ratio can be obtained in the frequency band 300-3400Hz, with a -6dBr output signal.

#### **III.3 - RECEIVE A/D SECTION**

The different functions included in the Rx A/D section are detailed hereafter. The format used at the digital interfaces of the Rx channel is two's complement encoded 16-bit.

#### III.3.1 - A/D Converter

The 128 (160, 192) oversampled A/D converter is based on a second order sigma-delta modulator. The signal to noise plus distortion ratio obtained for a signal spectrum limited to the 300-3400Hz telephone band, is typically 86dB with a -6dBr input signal.

#### III.3.2 - Decimation Filters

The 128 (160, 192) decimation is performed by two interpolating digital filters: FIR2 and IIR2, which are sampled at 128 x Fsx and 4 x Fsx (160 x Fsx and 5 x Fsx) (192 x Fsx and 6 x Fsx), respectively.

#### III.3.2.1 - FIR Filter (FIR2)

FIR2 is a finite impulse response decimating filter. Its sampling frequency is 128 x Fsx (or 160 x Fsx or 192 x Fsx) and its decimation ratio is 32. The Z transfer function of this FIR is:

$$H(z) = \left(\frac{1 - z^{-32}}{32 (1 - z^{-1})}\right)^3$$

with  $Z = \exp(j2\pi F/Txoclk)$ and Txoclk = 128 (160, 192) x Fsx

### III.3.2.2 - Programmable Decimation Filter (IIR2)

IIR2 is an infinite impulse response filter. It provides the low-pass filtering needed to remove the noise remaining above half the sampling frequency (e.g. 4800Hz) (see Figure 14). The output of the IIR2, RxTx, will be processed by the DSP. In "band split" mode (see Table 21), RxTx becomes the input signal to IIR3. The RxTx will always be available on serial interface (SSIA in Figure 2).

The IIR2 filter is a cascade of seven biquads. The filter coefficients are loaded into the associated RAM (38 x 13).

The filter transfer function has been made programmable in order to meet specific requirements. The sampling frequency is 4-times (5-times, 6-times) the down-sampling frequency selected for the Tx section (e.g. 9600 x 4Hz).

To support echo cancelling applications the clocks used for the A/D converter and the decimation filters are synchronized on the Tx system clock, i.e. on the Tx rate. It must be pointed out that using a single clock system in A/D and D/A conversions is important for reducing induced noise.

The 12+1 bit filter coefficients are loaded into the internal RAM2 and must be loaded from the serial bus. All 38 coefficients have to be loaded to implement an IIR transfer function.

### III.3.3 - Eye-diagram Display

Two 8-bit digital to analog converters are provided to monitor, on a CRT, the X and Y quadrature signals of the eye pattern related to the demodulated signal. The format of the data input is MSB first, 8-bit two's complement, and most significant byte for EYEY sample and least significant byte for the EYEX sample. The reference voltage of these two converters is the power supply voltage  $V_{DD}$ . The EYE pattern can be monitored on one or two Synchronous Serial Interface mode.

#### **III.4 - RECEIVE RECONSTRUCTION SECTION**

As the Rx channel sampling is synchronized to the Tx system clock, it is necessary to reconstruct the Rx signal in order to get samples synchronized to the Rx symbol rate recovered in the demodulator.

The function of the reconstruction filter (IIR3 and FIR3) is to oversample by 128 x Fsx (160 x Fsx,

192 x Fsx) the receive signal (ResSig) comming from the DSP after echo cancellation. The oversampled signal is then down-sampled at Fsr rate to make it available to the DSP as RxSig at SSIB or RxS1/RxS2 at SSIA (see section IV.1 and IV.2). The down sampling process does not introduce significant error.

The transfer function of the first section of the reconstruction filter is programmable in the same way as the Tx and Rx IIR filters previously described.

#### III.4.1 - Programmable Interpolation Filter (IIR3)

IIR3 is an infinite impulse response interpolating filter.

The purpose of this digital filter is to interpolate 4-times (5-times, 6-times) the digital signal from the DSP. This filter is sampled at 4-times (5-times, 6-times) the basic sampling frequency, (e.g. 9600 x 4 Hz).

The digital samples are encoded in 16-bit two's complement format.

The IIR3 filter is a cascade of seven biquads. The filter coefficients are loaded into the associated RAM (38 x 13). Each coefficient is coded into 12 bits and can be doubled by virtue of an extra bit. All 38 coefficients have to be loaded to implement an IIR transfer function.

This filter has been made programmable to offer each user the possibility to add filtering characteristics, e.g. highpass section or equalization, matched to a particular application.

For example, in a band-split MODEM application, the first section can be a wide channel band-pass filter (allowing the DSP to supervise boundary audio tones) and the second section can be dedicated to high band and low band splitting.

#### III.4.2 - FIR Filter (FIR3)

FIR3 is a finite impulse response interpolating filter. Its input sampling frequency is 4 x Fsx (5 x Fsx), (6x Fsx) and the interpolation ratio is 32. The Z transfer function of this FIR is :

$$H(z) = \left(\frac{1 - z^{-32}}{32 (1 - z^{-1})}\right)^{3}$$

with  $Z = \exp(j2\pi F/Txoclk)$ and Txoclk = 128 (160, 192) x Fsx

#### **III.5 - CLOCK GENERATION**

Master clock is obtained from either a crystal tied between pins XTAL10 (or XTAL11) and XTAL2 or from an external signal connected to the XTAL10 (or XTAL11) pin, in the latter case, the XTAL2 pin should be left open circuit.

Two external crystals (or two external master clock signals), software selectable one at a time, can be used to cope with complex applications. It is mandatory to shortcircuit XTAL10 and XTAL11 when a single external crystal or clock generator is used.

The crystal selection is done by bit D13 (QS) in TxCTRL word of the serial interface A.

Setting QS to 0 select the XTAL11 input and  $TxCLK = FQ / (N \times R \times S \times T \times CS)$  with CS = 8. Setting QS to 1 select the XTAL10 Input and  $TxCLK = FQ / (N \times R \times S \times T \times CS)$  with CS = 16.

To insure the start-up of the STLC7545, the XTAL10 input must always be tied to a crystal or an external clock signal, as that pin is automatically selected when powering-on the device.

The different transmit (Tx) and Receive (Rx) clocks are obtained by master clock frequency division in several programmable counters. The Tx and Rx clocks can be synchronized on external signals by performing phase shifts in the frequency division process (equivalent to adding or suppressing master clock transitions at the counter inputs). Two independant digital phase locked loops (DPLL) are

implemented using this principle, one for Tx and one for Rx.

Two clock modes are available, selected by the External Oversampling Clock Mode input pin (EOCMODE). When the EOCMODE pin is tied to the GND the internal clock mode is selected. In this mode all the clock are generated internally. When the EOCMODE pin is tied to  $V_{DD}$ , the External Oversampling Clock Mode is selected.

In external oversampling clock mode, the user must provide the chip with the oversampling frequency knowing the interpolation and the decimation ratios selected in the TxCR3 and RxCR3 register. It can be provided from the highest synchronous clock (TxHSCLK and RxHSCLK) using an external divider. In any case, the user will have to comply with the relation: Crystal frequency FQ must be greater than 470 x 4 x Fsx with an oversampling ratio of 128 or than 470 x 5 x Fsx with an oversampling ratio of 160 or than 470 x 6 x Fsx with an oversampling ratio of 192.

Several values can be chosen for the master clock frequency. The four frequencies given in table 1 are of particular interest, as they are compatible with standard Modem frequencies.

Note: In the remainder of the datasheet, unless otherwise indicated, 36.864MHz will be considered as the nominal master clock frequency. The maximum master clock frequency is 38MHz.

Table 1: List of usual frequency available

| Crystal<br>Frequency | Symbol Rate Frequency                                           | Bit Rate (bps)  | Sampling (bps)                 |

|----------------------|-----------------------------------------------------------------|-----------------|--------------------------------|

| FQ (MHz)             | Fbaud (baud)                                                    |                 | Fsx, Fsr (Hz) (1)              |

| 18.432 (2)           | 600, 1200, 1600, 2400                                           | All up to 19200 | 3,4,5,6,8,12 or 16 times Fbaud |

| 25.8048              | 600, 1200, 1600, 2400, 2800                                     | All up to 28800 | 3,4,5,6,8,12 or 16 times Fbaud |

| 29.4912 (2)          | 600, 1200, 1600, 2400                                           | All up to 19200 | 3,4,5,6,8,12 or 16 times Fbaud |

| 36.864 (3)           | 600, 1200, 1600, 2400, 2560, 2743, 2954, 3000, 3200, 3429, 3491 | All up to 38400 | 3,4,5,6,8,12 or 16 times Fbaud |

Notes: 1. Depending on the symbol rate frequency

Symbol rate =  $(2400 \times 16)/K$  with K = (16, 15, 14, 13, 12, 11)

Symbol rate =  $(2400 \times 8)/K$  with K = (8, 7, 6)

Symbol rate =  $(2400 \times 10)/K$  with K = (8, 7)

<sup>2. 7544</sup> like

<sup>3.</sup> This crystal frequency provides all the symbol rates satisfying the relation :

#### III.5.1 - Transmit DPLL

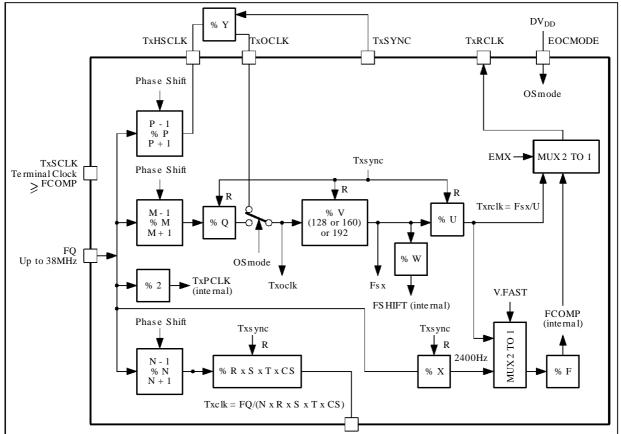

Frequency control of the Tx clock system (Figure 10) is obtained by performing additional up or down counting steps in the three input dividers M, N and P.

These elementary phase shifts of one master clock period are repeated at either the rate of the Fsx clock, or half that rate, depending on the required capture and tracking ranges (see Table 15 and 26).

The average updated frequency then varies between the following limits:

FQ - FSHIFT ≤ Faverage ≤ FQ + FSHIFT

Where FQ is the master clock frequency and FSHIFT equals Fsx or Fsx/2 (see table 26).

The TxDPLL phase comparison which determines lead or lag decisions, is simply obtained by sampling the synchronization clock, TxSCLK or RxCLK, on the falling edges of an internal clock taken from the division chain, FCOMP (see table 25). FCOMP frequency must be an integer submultiple of the synchronization clock. This frequency determines the Tx jitter magnitude. In V.34 synchronization mode FCOMP is equal to 2400Hz, and in 7544 mode the synchronization clock FCOMP can be chosen to be equal to the baud rate frequency. Only phase shifts of the same sense (lead or lag) are performed during each FCOMP period. The actual phase shifts during FCOMP period are given by the ratio

#### FSHIFT/FCOMP

These phase shifts are performed at the inputs of the M,N, and P dividers to lock the DPLL to the synchronisation signal (see Table 22).

If there is no transition on TxSCLK Pin, the Tx DPLL is free running.

To phase lock the TxDPLL there must be transistion on TxSCLK input within FCOMP period when programming TxCR2 register.

The Tx clock system may also run freely without any phase shift. In this case, the TxSCLK input is no longer active.

The DPLL capture and tracking range equals  $\pm$ FSHIFT/FQ. They have to be greater than  $\pm$  200ppm to comply with CCITT recommendations. FSHIFT = Fsx/2 minimizes the jitter. Because of this, there is a trade-off between higher capture and tracking ranges and lower jitter.

Ex : FQ = 36.864MHz and FSHIFT = 9600Hz. Capture and tracking range =  $\pm$  FSHIFT/FQ =  $\pm$  9600Hz/36.864MHz=  $\pm$  260ppm

# III.5.2. Transmit Clocks III.5.2.1 - Internal Mode

The internal clock mode is selected when the pin EOCMODE is tied to GND. In this mode the STLC7545 provides three Tx programmable synchronous modem clocks:

- a transmit bit rate clock TxCLK

- a transmit baud rate clock TxRCLK

- a transmit highest synchronous clock TxHSCLK, associated with the TxSYNC synchronization pulse, useful to generate additional clocks (e.g. extra divisors) if needed.

The outputs of the TxRCLK and TxHSCLK clocks, can be disabled when not used, but in 7544 synchronisation mode a correct baud rate frequency must be programmed as the FCOMP clock frequency depends on it.

The Tx clock system provides the sampling and oversampling clocks as well as the bit and synchro clocks (BCLKX and FSX) used by the serial interface A (SSI-A) described in section IV.

The counters of the Tx clock system (Figure 10) are automatically reset when powering-on the STLC7545 and when the NLPR input level is low. They can also be reset, under software control, during the following conditions:

- (1) on the next falling edge of the TxSCLK terminal clock or of the RxCLK receive bit rate clock (SST bit Table 22).

- (2) on the next falling edge of the TxRCLK transmit baud rate clock (baud chain clock reset) and in the next falling edge of FCOMP (bit chain clocks) when TxCR0, TxCR2 or TxCR3 register is accessed.

The case (1) gives the capability to speed-up the Tx DPLL synchronization; the case (2) is useful to fix the phase of the bit rate clock with respect to the baud rate clock, in particular after each modification of the bit or baud rate value.

The internally generated pulse resetting the Tx counters is output at the TxSYNC pin in order to synchronize external functions using the TxHSCLK clock.

#### III.5.2.2 - External Mode

The external clock mode is selected when the pin EOCMODE is tied to the  $V_{DD}.$  In this mode the user must provide the STLC7545 with the transmit oversampling clock. The internal DPLL can be used if the external transmit oversampling clock is generated by a divider synchronized by both the TxHSCLK and TxSync signals.

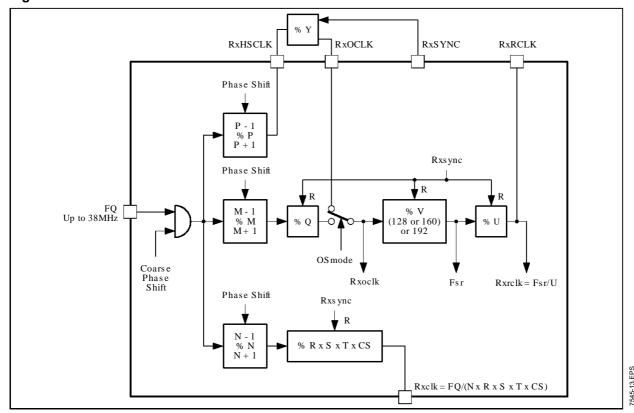

#### III.5.3 - Receive DPLL

The synchronization of the Rx counters delivering the Rx clocks (Figure 11) is performed by addition or suppression of master clock periods under DSP control. In this case, the phase comparison function of the RxDPLL is implemented in the associated DSP recovering the received symbols.

Two types of phase shift control are provided in the STLC7545:

- a coarse phase lag of programmable magnitude, obtained from the suppression of 64 to 4096 successive master clock transitions. This control is to be used to reduce the RxDPLL locking time.

- a fine phase lead or lag of programmable magnitude (i.e. 8 to 32 master clock periods or one Tx oversampling clock period) continuously used to implement the phase control loop. (see Table 38). Each elementary phase shift, corresponding to an addition or a subtraction of one master clock transition, is synchronized on an internal clock with frequency equal to the Rxoclk (128, 160 or 192 times the Rx sampling frequency Fsr). A phase shift is ,therefore, always completed in less than one Fsr period.

# III.5.4 - Receive Clocks III.5.4.1-Internal Mode

The internal clock mode is selected when the pin EOCMODE is tied to GND. In this mode the STLC7545 provides three Rx synchronous programmable modem clocks:

- receive bit rate clock RxCLK

- receive baud-rate clock RxRCLK

- receive highest synchronous clock, RxHSCLK associated with the RxSYNC synchronization pulse useful to generate additional clocks

The RxRCLK and RxHSCLK outputs can be disabled when not used. The bit rate clock frequency of the Rx modem can be chosen to be different from its Tx counterpart, provided Rx to Tx loopback is not required. The Rx clock system also provides the Rx sampling clock as well as the bit and synchro clocks (BCLKR and FSR) used by the serial interface B (SSI-B) described in section IV. The digital reconstruction filter implemented in the STLC7545 makes possible the choice of a receive nominal sampling frequency different from the transmit nominal sampling frequency. The counters of the Rx clock system (Figure 11) are reset when powering on the STLC7545 and when the NLPR input level is low. They can also be reset, under software control, on the next falling edge of the RxRCLK receive baud rate clock when the RxCR0, RxCR1 or RxCR3 register are accessed: this feature is used to fix the phase of the bit rate clock with respect to the baud rate clock, e.g. after each modification of the bit or baud rate value. The

internally generated pulse resetting the Rx counters is output at the RxSYNC pin in order to be used with the RxHSCLK clock.

#### III.5.4.2 - External Mode

The external clock mode is selected when the pin EOCMODE is tied the  $V_{DD}$ . In this mode the user must provide the STLC7545 with the receive oversampling clock. The internal DPLL can be used if the external receive oversampling clock is generated by a divider synchronized by both the RxHSCLK and RxSync signals.

# III.6 - SERIAL INPUT/OUTPUT SYNCHRONOUS INTERFACES

The STLC7545 has two Synchronous Serial Interfaces ports, SSIA and SSIB. They allow independent transmit and receive paths. Through the two serial ports, the STLC7545 can talk to various digital signal processors. The various serial interface signals and internal registers are given below:

#### SSI PORT A (SSIA)

- Transmit Frame Synchronization output (FSX)

- Transmit Bit clock output (BCLKX)

- Transmit Serial Data input (TxDI)

- Transmit input Shift Register (TSRIN)

- Transmit input Buffer Register (TBRIN)

- Transmit output Shift Register (TSROUT)

- Transmit Serial Data output (TxDO)

#### SSI PORT B (SSIB)

- Receive Frame Synchronization output (FSR)

- Receive Bit clock output (BCLKR)

- Receive Serial Data input (RxDI)

- Receive input Shift Register (RSRIN)

- Receive input Buffer Register (RBRIN)

- Receive output Shift Register (RSROÚT)

- Receive Serial Data output (RxDO)

#### **INPUT MODES**

- Synchronous Serial Interface Mode (SSIM)

- Bit Frame Rate Select (BFRS)

With SSIM input, the user can choose either single interface mode or dual interface mode. In single interface mode (section IV.2), only port SSIA is operational. Where as in dual interface mode (section IV.1), both SSIA and SSIB ports are operational. These two ports carry data inside a synchronous frame consisting of four/five or eight/ten sixteen bit time slots (only the four first time slots are used for transporting information. SSIA port is synchronous to the Tx system clock and SSIB port is synchronous to Rx system clock. The format of the signal samples carried on these port is two's complement with MSB sent or received first. As explained hereafter it is also possible to use the port A only to transfer the data between the STLC7545 and the associated DSP.

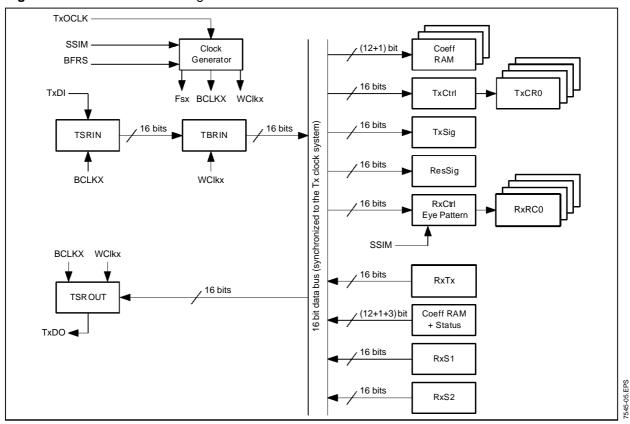

# III.6.1 - Tx Clock Related Registers

Figure 3: Tx Clocks Related Registers

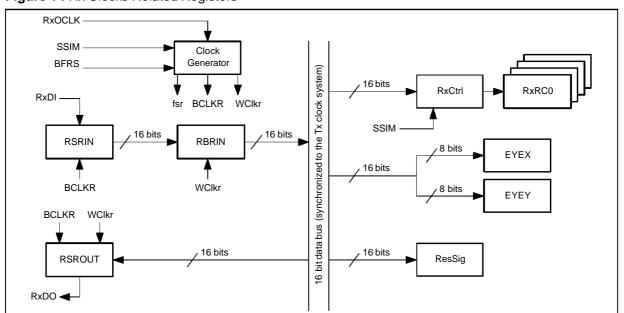

# III.6.2 - Rx Clock Related Registers

Figure 4: Rx Clocks Related Registers

#### IV - SERIAL INTERFACE OPERATION

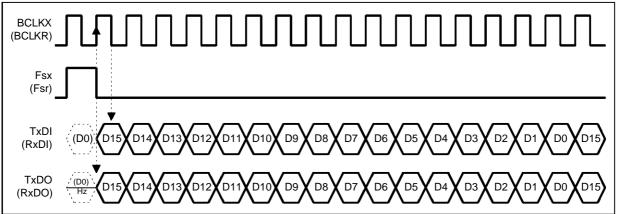

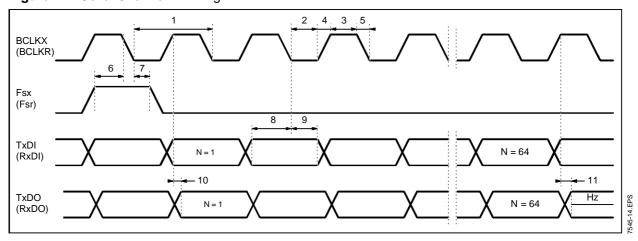

Serial data transmission (reception) is initiated by a frame synchro signal FSX (FSR). The Data is clocked from TxDI (RxDI) into TSRIN (RSRIN) on the falling edge of BCLKX (BCLKR) and transfered to the TBRIN (RBRIN) register when a complete 16 bit word has been received. Data is assumed to be received MSB first.

Serial data transmission (reception) output is initiated by a frame synchro signal FSX (FSR). The 16-bit Data word is loaded into TSROUT (RSROUT) and serially clocked out of TSROUT (RSROUT) to TxDO (RxDO) on the rising edge of BCLKX (BCLKR).

BCLKX (BCLKR) frequency can be programmed to be either 64 or 128 (80 or 160) (90 or 192) times Fsx (Fsr) using the Bit Frame Select (BFRS) input pin. This mean that the frame contains four, five,

six, eight, ten or twelve time slots of 16 bits. The time slots used for circuit operation are indicated in the next paragraph.

#### IV.1 - DUAL SERIAL INTERFACE MODE (SSIA, SSIB)

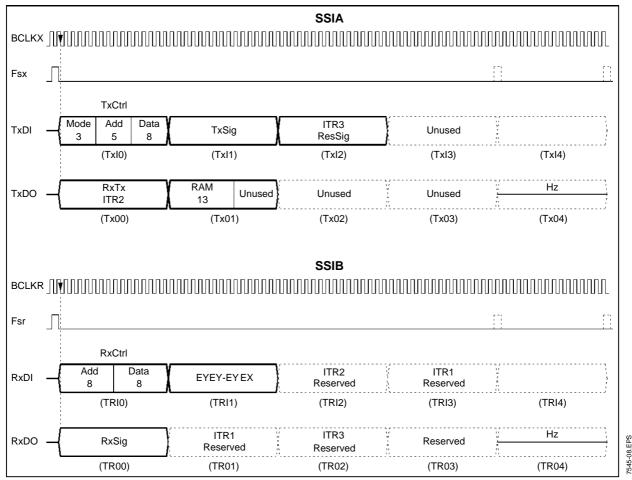

When SSIM is tied to  $V_{DD}$ , both A and B ports are functional: port A (SSIA) is dedicated to the Tx channel and port B (SSIB) to the Rx channel. The timing diagram showing the data format is given in Figures 5 and 6.

The time-slot TXO1 is dedicated to RAM coefficient reading. The RAM coefficient is selected by the address bits RA0 to RA1 in the TxCtrl word (see Table 4). Reading is initiated by the rising edge of Start bit Stb (bit D14 in Table 3) in the TxCtrl word.

Note: RxSig is also available in two time slot RxS1 and RxS2 on the time slot TxO2 and TxO3 on SSIA (see section IV.2)

Figure 5: Serial Channel Timing

5-07.EPS

Figure 6: Serial Channel Timing. Dual Port Mode

#### **IV.2 - SINGLE SERIAL INTERFACE MODE**

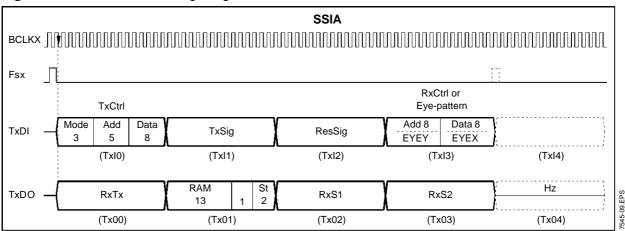

When SSIM is tied to GND, only port A (SSIA) is selected. In this case, port A carries both Tx and Rx signal samples and control words at Tx sampling rate (Fsx).

The RxDI input should be tied to V<sub>DD</sub>. Since port B is not functional in this mode, the RxSig (synchronized to Fsr) will be available in the two time slots, RxS1 and RxS2, synchronized to Fsx.

The reason for the two time slots is that the Fsr could be different in magnitude and phase from the Fsx.

The status bit St0 and St1 are used to indicate which of the RxS1 and RxS2 are valid. Please see the table following. For example, if Fsx = 9600Hz and Fsr = 14400Hz both RxS1 and RxS2 could carry valid data. Figure 7 shows the timing diagram.

The time-slot TXO1 is dedicated to RAM coefficient reading. The RAM coefficient is selected by address bits (RA0 to RA1) in the TxCtrl word (see Table 4). Reading is initiated by the rising edge of a Start bit Stb (bit D14 in Table 3) in the TxCtrl word. The time-slot Txl3 is dedicated to the RxCtrl word or the EYE-PATTERN, selected in the TxCtrl (see Table 5).

Table 2

|     | STATUS WORD IN TxO1 TIME SLOT |                   |  |  |  |  |  |  |  |  |  |

|-----|-------------------------------|-------------------|--|--|--|--|--|--|--|--|--|

| D1  | D0                            | Valid Data        |  |  |  |  |  |  |  |  |  |

| St1 | St0                           |                   |  |  |  |  |  |  |  |  |  |

| 0   | 0                             | None              |  |  |  |  |  |  |  |  |  |

| 0   | 1                             | None              |  |  |  |  |  |  |  |  |  |

| 1   | 0                             | RxS2              |  |  |  |  |  |  |  |  |  |

| 1   | 1                             | RxS1 and RxS2 (1) |  |  |  |  |  |  |  |  |  |

Note 1: The RxS1 sample precedes the RxS2 sample.

Figure 7: Serial Channel Timing. Single Port Mode

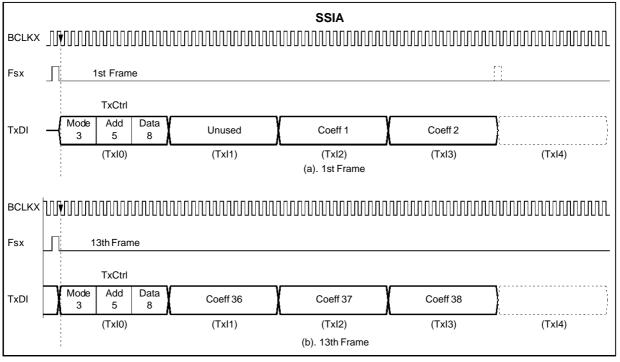

#### **IV.3 - COEFFICIENT LOADING MODE**

The Coefficient Loading Mode is selected by the Mode Select bit (MS) in the TxCtrl Word (Table 3). When the MS bit is a logic "1" the loading mode is selected. The IIR RAMS (RAM1 to RAM3) are selected in the TxCtrl word by two address bits (RAO to RA1). Each coefficient RAM stores 38 coefficients of 13 bits. Therefore the size of the coefficient RAM is 38 x 16 bits. The first frame transfers 2 coefficients and the 12 following frames

each transfer 3 coefficients into the selected RAM, as shown in Figure 8. The transfer is initiated by the rising edge of the Start bit coefficient Stb which is loaded into the TxCtrl word. When the coefficient loading mode is selected all data path are fixed to zero.

**Notes:** 1. Coefficient loading is the same for both dual and single interface modes.

In coefficient loading mode , the EYE-PATTERN (time slot TxI3) (and the RxCtrl in a single serial interface) cannot be accessed

Figure 8: Coefficient Loading Mode

7545-10.EPS

#### **IV.4 - COEFFICIENT READING**

Coefficient reading is selected in DATA mode only, i.e. when the Mode Select bit (MS) in the TxCtrl word is tied to logical 0. The IIR RAMS (RAM1 to RAM3) are selected in the TxCtrl word by two address bits (RA0 to RA1). The 38 coefficients of 13 bits are available, one per frame, in the timeslot TxO1 on the output Tx port A (see Figures 6, 7). The reading is available on the rising edge of the Start bit Stb loaded into the TxCtrl word. The first coefficient is output with one frame of delay on TxO1.

#### IV.5 - CRYSTAL SELECTION (XTAL10, XTAL11)

For application needing different or higher symbol rates, the user can software select different master clock frequencies for the STLC7545. Two XTAL inputs are provided for this purpose. The active XTAL input is selected in the time slot Txl1 with the Quartz Select bit (QS). It is mandatory to shortcircuit the XTAL10 and XTAL11 inputs when a single external crystal or clock generator is used.

#### IV.6 - FRAME FREQUENCY PROGRAMMING

When using the nominal master clock frequency, the frame frequency can be from 7200Hz to 16000Hz (see Tables 15 and 32). Whenever the frame frequency Fsx (Fsr) is modified, the data to the STLC7545 during that frame should be high in the time slots Txl1 (Rxl1), Txl2 (Rxl2) and Txl3

(RxI3). This is because the BCLKX (BCLKR) during that frame may not be correct. Therefore, whenever the Fsx (Fsr) is changed the user has to send information to the STLC7545 after one frame delay.

# IV.7 - INITIALIZATION AND LOW-POWER RESET MODE

Internal power-on circuitry automatically resets the DPLL, the clock generator counters, and initializes the internal control registers. The clocks affected are the symbol clock, the bit clock and the sampling clock. The initial status of these registers is given in the PROGRAMMABLE FUNCTIONS section. The transmit attenuator is initialized to an infinite attenuation mode (see Table 24) to avoid the transmission of undesirable signals on the phone line.

During hardware low power reset (NLPR pin is tied to GND), the input of the inverter (across the crystal) will be high (DVDD), the DPLLs and the clock generator counters are initialized, all the analog circuitry is placed in low-power mode and the XTAL oscillator is stopped.

Access to the circuit is disabled during reset until the clock oscillator starts. The duration of the reset time can be increased by connecting the NLPR input to an external RC timeconstant as indicated in Figure 9.

In normal operation the NLPR input is used to control the LowPower mode. When NLPR is not used, it must be tied to  $V_{DD}$ .

Figure 9: Power-on Initialization Circuitry

#### **V - CIRCUIT PROGRAMMING**

This section defines the control and status words required to program the STLC7545.

The circuit configuration is managed by the control words TxCtrl and RxCtrl and the SSIM, BFRS inputs. The control words contain three fields:

- Mode Field 3 bits (D15-D13) mode control bit

- Address Field 5 bits (D12-D8) 2 bits for Coeff Ram address

3 bits for Control Registers address

- Data Field 8 bits (D7-D0) Control Registers content

# V.1 - MODE FIELD

Table 3: Mode Field

|     | TxCtrl Word |     |                                                                                                                                              |  |  |  |  |  |  |  |

|-----|-------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| D15 | D14         | D13 | Select mode                                                                                                                                  |  |  |  |  |  |  |  |

| MS  | Stb         | QS  |                                                                                                                                              |  |  |  |  |  |  |  |

| 0   | -           | -   | Data Mode and Control Register access mode                                                                                                   |  |  |  |  |  |  |  |

| 1   | -           | -   | Coefficient Loading Mode and Filter Data Memory Reset (INI)                                                                                  |  |  |  |  |  |  |  |

| -   | 1           | -   | Start bit for Coefficient Loading or Reading. The loading is initiated by a rising edge, i.e. a logical one programmed after a logical zero. |  |  |  |  |  |  |  |

| -   | -           | 1   | XTAL10 Selected (INI) (CS equals 16 in bit chain clock)                                                                                      |  |  |  |  |  |  |  |

| -   | -           | 0   | XTAL11 Selected (CS equals 8 in bit chain clock)                                                                                             |  |  |  |  |  |  |  |

INI: initial value

# V.2 - ADDRESS FIELD V.2.1 - RAM Address Field

Table 4: RAM Address Field

|     | TxCtrl Word |     |     |     |     |     |     |                |  |  |  |  |  |

|-----|-------------|-----|-----|-----|-----|-----|-----|----------------|--|--|--|--|--|

| D15 | D14         | D13 | D12 | D11 | D10 | D9  | D8  | RAM Address    |  |  |  |  |  |

| MS  | Stb         | QS  | RA0 | RA1 | AD2 | AD1 | AD0 |                |  |  |  |  |  |

| -   | 1           | -   | 0   | 0   | -   | -   | -   | RAM 1 (INI)    |  |  |  |  |  |

| -   | 1           | -   | 0   | 1   | -   | -   | -   | RAM 2          |  |  |  |  |  |

| -   | 1           | -   | 1   | 0   | -   | -   | -   | RAM 3          |  |  |  |  |  |

| -   | -           | -   | 1   | 1   | -   | -   | -   | Not RAM access |  |  |  |  |  |

INI: initial value

# V.2.2 - Transmit Control Register Address Field

Table 5: Transmit Control Register Address Field

| Register Name       | TxCtrl Word (2) |     |     |     |     |     |     |       |  |  |  |

|---------------------|-----------------|-----|-----|-----|-----|-----|-----|-------|--|--|--|

|                     | D15             | D14 | D13 | D12 | D11 | D10 | D9  | D8    |  |  |  |

|                     | MS              | Stb | QS  | RA0 | RA1 | AD2 | AD1 | AD0   |  |  |  |

| TxCR0 (1)           | -               | -   | -   | -   | -   | 0   | 0   | 0     |  |  |  |

| TxCR1 (1)           | -               | -   | -   | -   | -   | 0   | 0   | 1     |  |  |  |

| TxCR2               | -               | -   | -   | -   | -   | 0   | 1   | 0     |  |  |  |

| TxCR3 (1)           | -               | -   | -   | -   | -   | 0   | 1   | 1     |  |  |  |

| None                | -               |     |     |     |     | 1   | 1   | 1     |  |  |  |

| EYE Pattern on TxI3 |                 |     |     |     |     | 1   | 1   | 0 (3) |  |  |  |

Notes: 1. A reset is generated when programming these registers (see III.5.2.1).

2. No register access for the non-specified code

3. In single interface mode only

# V - CIRCUIT PROGRAMMING (continued)

# V.2.3 - Receive Control Register Address Field

Table 6: Receive Control Register Address Field

| Register Name  |     | RxCtrl Word (2, 3) |     |     |     |     |     |     |  |

|----------------|-----|--------------------|-----|-----|-----|-----|-----|-----|--|

|                | D15 | D14                | D13 | D12 | D11 | D10 | D9  | D8  |  |

|                | -   | -                  | -   | -   | -   | AD2 | AD1 | AD0 |  |

| RxCR0 (Note 1) | -   | -                  | -   | -   | -   | 0   | 0   | 0   |  |

| RxCR1 (Note 1) | -   | -                  | -   | -   | -   | 0   | 0   | 1   |  |

| RxCR2          | -   | -                  | -   | -   | -   | 0   | 1   | 0   |  |

| RxCR3 (Note 1) | -   | -                  | -   | -   | -   | 0   | 1   | 1   |  |

| None           | -   | -                  | -   | -   | -   | 1   | 1   | 1   |  |

- Notes: 1. A reset is generated when programming the RxCR0, RxCR1 and RxCR3 registers, this reset is synchronous with the falling edge of the Rx symbol clock.

- 2. In single interface mode, the RxCtrl registers cannot be programmed during the coefficient loading mode (see Figures 7 and 8).

- 3. No register access for the non-specified code

#### **V.3 - CONTROL REGISTER DATA FIELD**

# V.3.1 - Transmit Control Register Programming

Table 7: Transmit Control Register Programming

| Register |     |     |     | Da | ata |     |     | Programmed Function |                                                                                                                                    |

|----------|-----|-----|-----|----|-----|-----|-----|---------------------|------------------------------------------------------------------------------------------------------------------------------------|

|          | D7  | D6  | D5  | D4 | D3  | D2  | D1  | D0                  |                                                                                                                                    |

| TxCR0    | N0  | R1  | R0  | S1 | S0  | T2  | T1  | T0                  | Tx Bit rate clock generator                                                                                                        |

| TxCR1    | MO  | Q1  | Q0  | U2 | U1  | U0  | P0  | BS                  | Tx Sampling, Baud and HS clock generators; Band Split configuration.                                                               |

| TxCR2    | AT1 | AT0 | LTX | LC | SST | R3  | VF  | R2                  | Tx Attenuator, TxClock Synchronization, V.Fast Synchronization mode, Divider by 12/11 Bit clock                                    |

| TxCR3    | V2  | V1  | V0  | W  | HQ1 | HQ0 | Ts0 | DL                  | Tx Sampling (used with TxCR1), FCOMP and FSHIFT frequency programming HALF-INTEGER Q DIVIDER (used with TxCR1), Test configuration |

# V.3.2 - Receive Control Register Programming

Table 8: Receive Control Register Programming

| Register |    |     |     | Da  | ata |     |     | Programmed Function |                                                                                                                                                                 |

|----------|----|-----|-----|-----|-----|-----|-----|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          | D7 | D6  | D5  | D4  | D3  | D2  | D1  | D0                  |                                                                                                                                                                 |

| RxCR0    | N0 | R1  | R0  | S1  | S0  | T2  | T1  | T0                  | Rx Bit rate clock generator                                                                                                                                     |